# JVC

# **SERVICE MANUAL**

COMPACT COMPONENT MD SYSTEM

# CA-MXS6MDR SP-MXS6MD

# **MDLP**

| CA-MXS6MDR | MAIN SYSTEM    |

|------------|----------------|

| SP-MXS6MD  | SPEAKER SYSTEM |

| Area Suffix                                                       |  |  |

|-------------------------------------------------------------------|--|--|

| B ······ U.K. E ····· Continental Europe EN ····· Northern Europe |  |  |

### **Contents**

| Safety precautions 1-2            | Maintenance of laser pickup (MD) 1-38 |

|-----------------------------------|---------------------------------------|

| Preventing static electricity 1-4 | Replacement of laser pickup (MD) 1-38 |

| Important for laser products 1-5  | Flow of functional operation          |

| Disassembly method 1-6            | until TOC read (CD section) 1-39      |

| Adjustment method ····· 1-31      | Maintenance of laser pickup (CD) 1-40 |

| Flow of functional operation      | Replacement of laser pickup (CD) 1-40 |

| until TOC read (MD section) 1-37  | Description of major ICs1-41          |

|                                   |                                       |

# Safety Precautions-

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

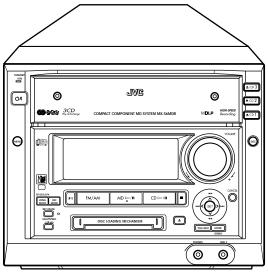

- 5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

- ◆ Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.)

- Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a  $1,500\Omega$  10W resistor paralleled by

a 0.15  $\mu$ F AC-type capacitor between an exposed metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. voltage measured Any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

# Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

AUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

# Safety precautions (U.K only) -

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits.

- 2. Any unauthorised design alterations or additions will void the manufacturer's guarantee; furthermore the manufacturer cannot accept responsibility for personal injury or property damage resulting therefrom.

- 3. Essential safety critical components are identified by ( \( \underset \) ) on the Parts List and by shading on the schematics, and must never be replaced by parts other than those listed in the manual. Please note however that many electrical and mechanical parts in the product have special safety related characteristics. These characteristics are often not evident from visual inspection. Parts other than specified by the manufacturer may not have the same safety characteristics as the recommended replacement parts shown in the Parts List of the Service Manual and may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

# Warning -

- 1. Service should be performed by qualified personnel only.

- 2. This equipment has been designed and manufactured to meet international safety standards.

- 3. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 4. Repairs must be made in accordance with the relevant safety standards.

- 5. It is essential that safety critical components are replaced by approved parts.

- 6. If mains voltage selector is provided, check setting for local voltage.

<u>AUTION</u> Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

# **Preventing static electricity**

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

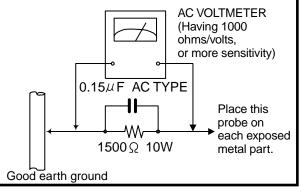

## 1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as CD/MD players. Be careful to use proper grounding in the area where repairs are being performed.

#### 1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

### 1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

### 1.1.3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

# 1.2. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

# Important for laser products

#### 1.CLASS 1 LASER PRODUCT

- **2.DANGER:** Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION:** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

- 4.CAUTION: The compact disc player uses invisible laserradiation and is equipped with safety switches whichprevent emission of radiation when the drawer is open and the safety interlocks have failed or are de feated. It is dangerous to defeat the safety switches.

**5.CAUTION**: If safety switches malfunction, the laser is able to function.

**6.CAUTION**: Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

**VARNING**: Osynlig laserstrålning är denna del är öppnad och spårren är urkopplad. Betrakta ej strålen.

VARO : Avattaessa ja suojalukitus ohitettaessa olet alttiina näkymättömälle lasersäteilylle.Älä katso säteeseen.

ADVARSEL: Usynlig laserstråling ved åbning, når sikkerhedsafbrydere er ude af funktion. Undgå udsættelse for stråling.

ADVARSEL: Usynlig laserstråling ved åpning,når sikkerhetsbryteren er avslott. unngå utsettelse for stråling.

### REPRODUCTION AND POSITION OF LABEL

### **WARNING LABEL**

CLASS 1 LASER PRODUCT

DANGER: Invisible laser radiation when open and interlock or defeated. AVOID DIRECT EXPOSURE TO BEAM (e)

VARNING : Osynlig laserstrålning är denna del är öppnad och spårren är urkopplad. Betrakta ej strålen. (s) VARO: Avattaessa ja suojalukitus ohitettaessa olet alttiina näkymättömälle lasersäteilylle.Älä katso säteeseen. (d)

ADVARSEL: Usynlig laserstråling ved åbning, når sikkerhedsafbrydere er ude af funktion. Undgå udsættelse for stråling. (f)

# **Disassembly method**

### <Main body>

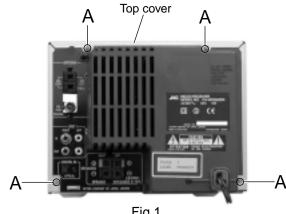

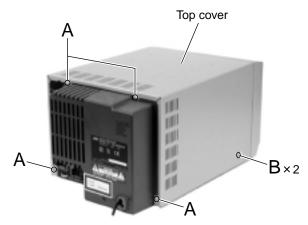

### ■ Removing the top cover

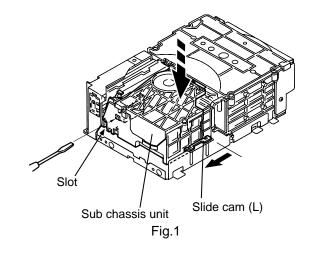

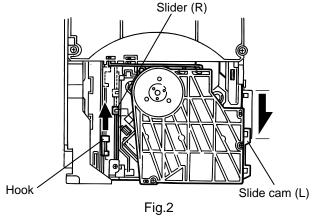

(See Fig. 1 and 2)

- 1. Remove the four screws **A** on the back of the body.

- 2. Remove the two screws **B** on both sides of the body.

- 3. Lift up the rear part of the top cover while pulling both sides, then remove the top cover.

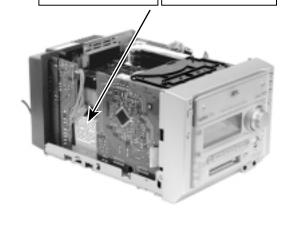

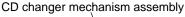

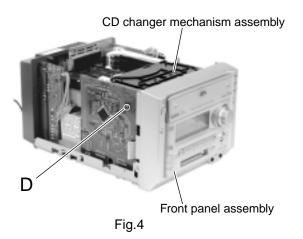

- · Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the card wire from connector CN661 on the input board.

- 2. Remove the four screws C on the upper side of the body.

- 3. Remove the screw **D** on the left side of the body.

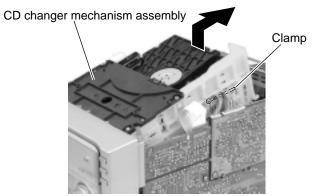

- 4. Release the wires from the clamp on the right side of the CD changer mechanism assembly. Lift up the rear part of the CD changer mechanism assembly and pull out it from the front assembly.

Fig.1

Fig.2

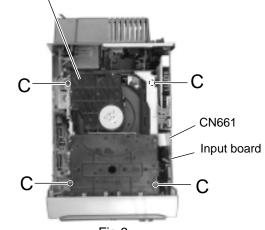

Fig.5

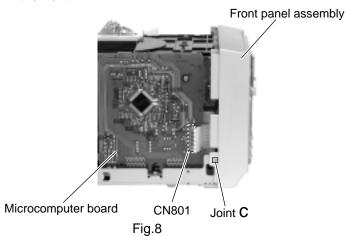

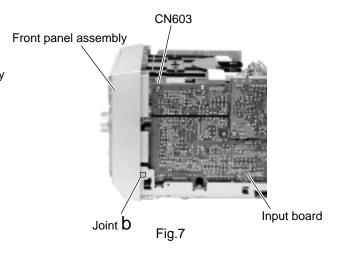

# ■Removing the font panel assembly (See Fig.6 to 8)

- Prior to performing the following procedure, remove the top cover.

- Disconnect the wire from connector CN603 on the input board and the card wire from CN801 on the microcomputer board.

- 2. Remove the two screws **E** on the bottom of the body.

- 3. Release the joint a on the bottom and the two joints b and c on the lower sides of the body using a screwdriver. Detach the front panel assembly toward the front.

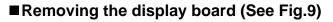

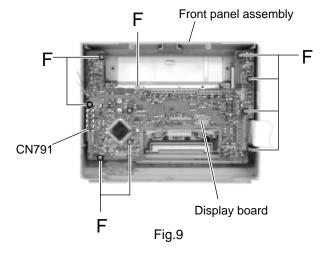

- Prior to performing the following procedure, remove the top cover and the front panel assembly.

- 1. Remove the nine screws **F** attaching the display board to the front panel assembly.

- 2. Disconnect connector CN791 on the display board from the control board on the front panel assembly.

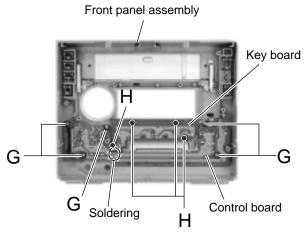

# ■Removing the control board / the key board (See Fig.10)

- Prior to performing the following procedure, remove the top cover, the front panel assembly and the display board.

- Remove the five screws G and the four screws H attaching the control board and the key board.

REFERANCE: When removing the control board and the key board respectively, unsolder each board.

Fig.6

Fig.10

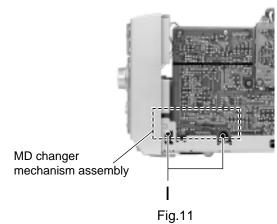

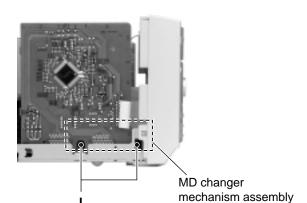

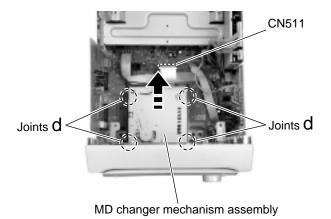

# ■ Removing the MD changer mechanism (See Fig.11 to 13)

- Prior to performing the following procedure, remove the top cover and the CD changer mechanism assembly.

- Disconnect the card wire from connectors CN511 on the main board.

- 2. Remove the four screws I on both sides of the body.

- 3. Pull out the MD changer mechanism assembly from behind upward while releasing the four joints **d** using a screwdriver.

Fig.12

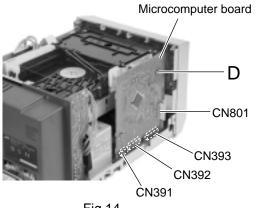

# ■Removing the microcomputer board (See Fig.14)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the card wire from connector CN801 on the microcomputer board.

- Remove the screw **D** attaching the microcomputer board.

- 3. Disconnect the lower connector CN391, CN392 and CN393 from the main board by pulling them.

Fig.13

Fig.14

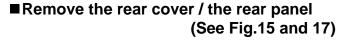

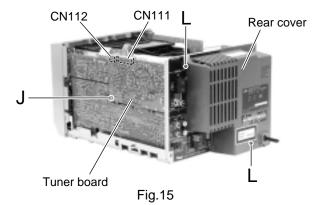

# ■Removing the tuner board (See Fig.15 and 16)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the wire from connector CN111 and CN112 on the tuner board.

- 2. Remove the screw **J** on the side of the body.

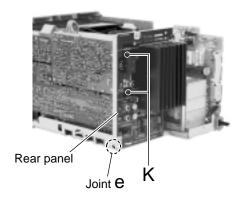

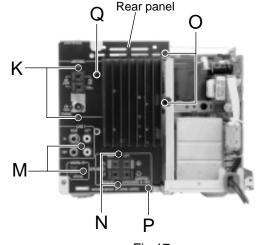

- Remove the two screws K on the back of the rear panel.

REFERANCE: To facilitate the procedure, remove the rear panel in advance.

- Prior to performing the procedure, remove the top cover.

- 1. Remove the two screws **L** attaching the rear cover to the body.

- 2. Remove the two screws **K**, **M**, **N**, **O**, and the screw **P** and **Q** respectively.

- 3. Release the joint **e** on the lower left side of the rear panel.

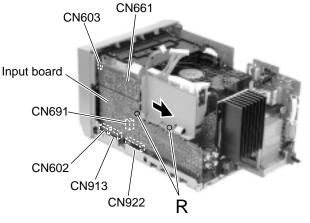

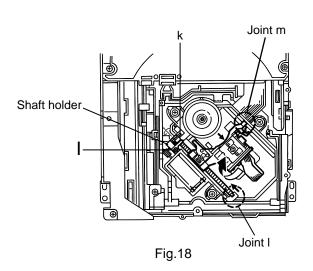

# ■Removing the Input board (See Fig.18)

- Prior to performing the procedure, remove the top cover, the rear cover, the rear panel and the tuner board.

- 1. Disconnect the card wire from connector CN661 and the wire from CN603 on the input board.

- 2. Remove the two screws **R** attaching the bracket and remove the bracket in the direction of the arrow.

- Disconnect the lower connector CN602, CN913 and CN922 from the main board. Disconnect the wire from CN691 on the input board.

Fig.16

Fig.17

Fig.18

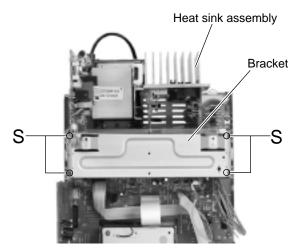

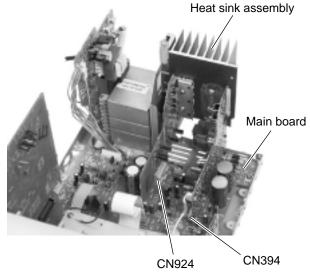

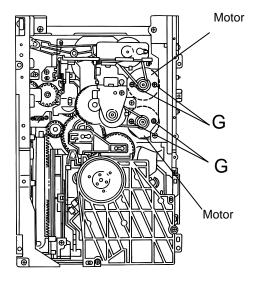

# ■ Removing the heat sink assembly (See Fig.19 and 20)

- Prior to performing the procedure, remove the top cover, the CD changer mechanism assembly, the rear cover, the rear panel, the tuner board and the input board.

- 1. Remove the four screws **S** attaching the bracket.

- Disconnect connector CN924 and CN394 from the main board.

Fig.19

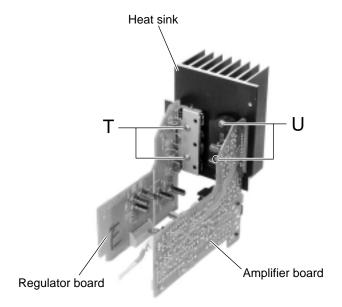

# ■Removing the regulator board / the amplifier board (See Fig.21)

- Prior to performing the procedure, remove the top cover, the CD changer mechanism assembly, the rear cover, the rear panel, the tuner board, the input board and the heat sink assembly.

- 1. Remove the two screws **T** or **U** attaching the regulator board and the amplifier board to the heat sink.

Fig.20

Fig.21

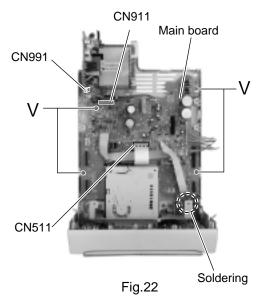

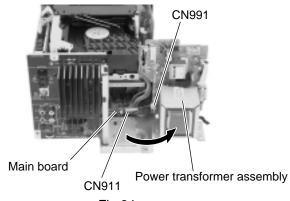

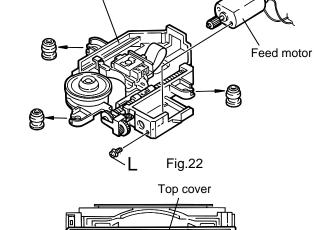

### ■ Removing the Main board (See Fig.22)

- Prior to performing the procedure, remove the top cover, the CD changer mechanism assembly, the rear cover, the rear panel, the tuner board, the input board and the heat sink assembly.

- 1. Disconnect the wire from connector CN911 on the main board and CN991 on the power transformer assembly.

- 2. Disconnect the card wire from connector CN511 on the main board.

- 3. Remove the four screws V attaching the main board.

- 4. If necessary, unsolder the wire on the headphone

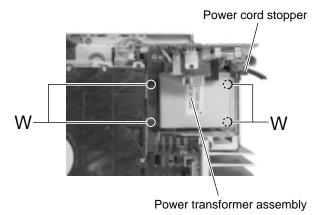

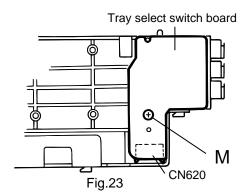

#### ■Removing the power transformer assembly (See Fig.23 and 24)

- · Prior to performing the following procedure, remove the top cover and the rear cover.

- 1. Remove the four screws W attaching the power transformer assembly.

- 2. Pull out the power cord stopper from the body upward. Turn the power transformer assembly while lifting it as shown in the figure.

- 3. Disconnect the wire from connector CN911 on the main board and CN991 on the power transformer board. Remove the power transformer assembly from the body.

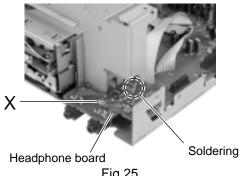

# ■Removing the headphone board (See Fig.25)

- Prior to performing the procedure, remove the top cover, the CD changer mechanism assembly, the front panel assembly, the rear cover, the rear panel, the tuner board and the input board.

- 1. Remove the screw X attaching the headphone board.

If necessary, unsolder the wire on the headphone board.

Fig.23

Fig.24

Fig.25

#### <MD section>

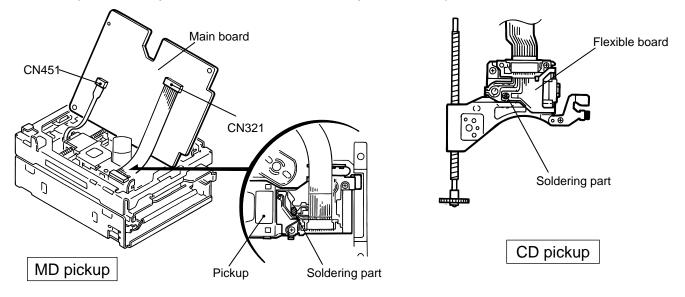

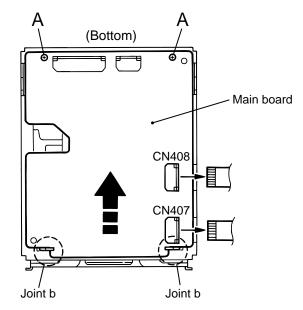

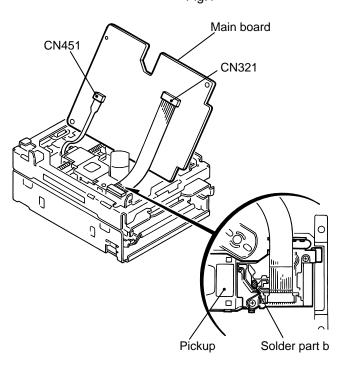

# ■Removing the main board (See Fig.1 and 2)

- 1. Turn over the body and disconnect the card wire from connector CN408 and the flexible wire from CN407 on the main board.

- 2. Remove the two screws A attaching the main board. Slide the main board in the direction of the arrow to release the two joints a with the single flame.

- 3. Solder part b on the pickup in the body. Disconnect the flexible harness from connector CN321 and CN451 on the underside of the main board. Then remove the main board.

Fig.1

Fig.2

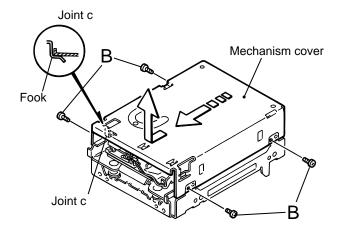

# ■Removing the mechanism cover (See Fig.3)

- 1. Remove the four screws B on both sides of the body.

- 2. Move the mechanism cover toward the front to disengage the front hook of the mechanism cover from the internal loading assembly (Joint c). Then remove the mechanism cover upward.

Fig.3

# ■Removing the head lifter (See Fig.4 to 6)

1. Move the head lifter on top of the body in the direction of the arrow and turn around.

2. Detach the spring from the hook of the body. Remove the head lifter with the spring.

3. If necessary, remove the spring from the head lifter.

Fig. 4

Head lifter

Fig. 5

Fig. 6

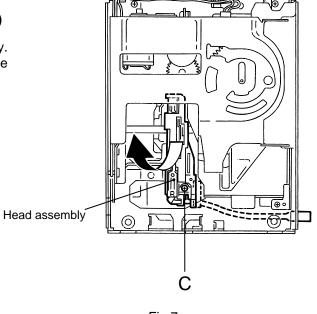

# ■Removing the head assembly (See Fig.7)

1. Remove the screw C on the upper side of the body. Remove the head assembly while pulling the flexible harness from the body.

Fig.7

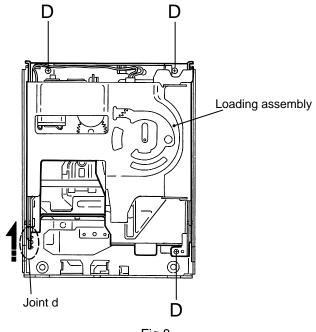

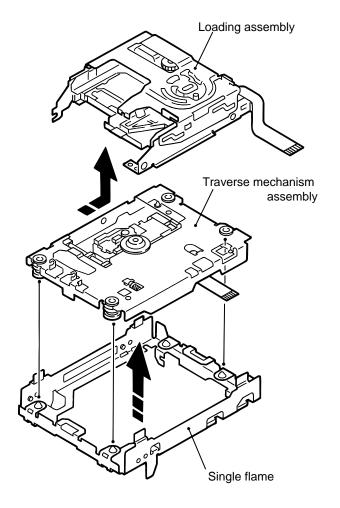

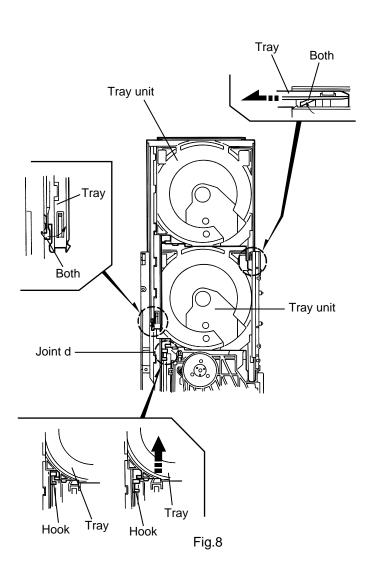

# ■Removing the Loading assembly (See Fig.8 and 9)

Ref: The loading assembly, the traverse mechanism assembly and the single flame will be removable after removing the loading assembly from the body.

- Prior to performing the following procedure, remove the main board, the mechanism cover, the head lifter and the head assembly.

- 1. Remove the three screws D on the upper side of the body.

- 2. Move the loading assembly forward to disengage it from the traverse mechanism assembly (Joint d). Then remove it upward.

- 3. Remove the traverse mechanism assembly from the single flame.

Fig.9

### <Loading assembly>

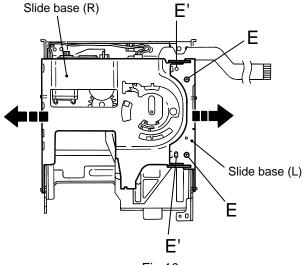

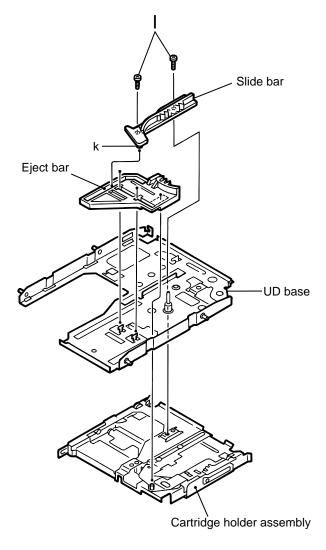

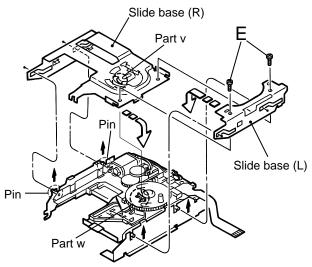

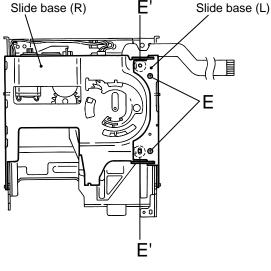

# ■Removing the slide base (L) / (R) (See Fig.10)

- 1. Remove the two screws E on the upper side of the loading assembly.

- 2. Remove the slide base (L) outward. (Release it from the joint bosses E.)

- 3. Remove the slide base (R) outward.

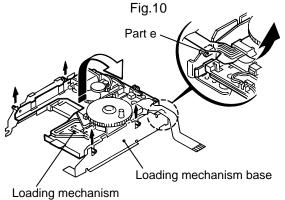

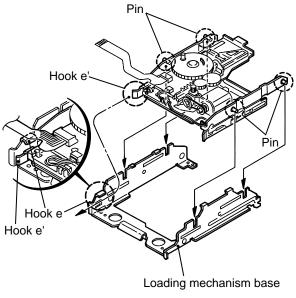

# ■Removing the loading mechanism assembly (See Fig.11)

Detach the loading mechanism assembly upward to release the four pins on both sides from the loading motor, paying attention to the part e of the loading mechanism base.

Loading mechanism assembly Fig.11

## —Loading mechanism assembly —

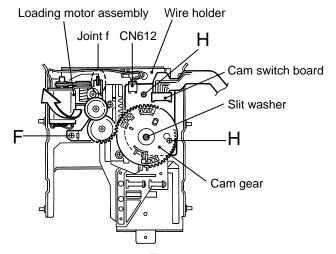

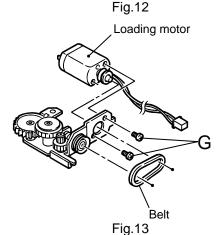

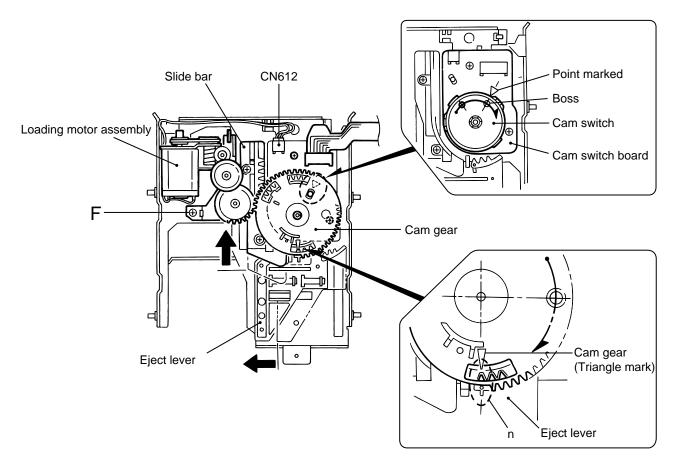

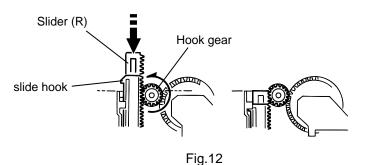

# ■Removing the loading motor (See Fig.12 and 13)

- 1. Disconnect the harnesses from the wire holder and from connector CN612 on the cam switch board.

- 2. Remove the screw F attaching the loading motor and release the joint f.

- 3. Remove the belt from the loading motor assembly.

- Remove the two screws G attaching the loading motor.

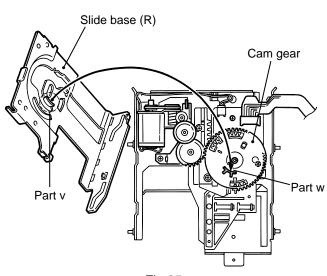

# ■Removing the cam gear and the cam switch board (See Fig.12)

- Remove the slit washer attaching the cam gear and pull out the cam gear.

- 2. Disconnect the harness from the wire holder and from connector CN612 on the cam switch board.

- 3. Remove the two screws H and the clamp. Remove the cam switch board.

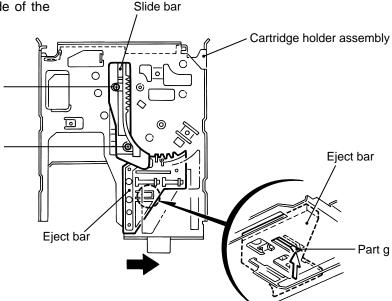

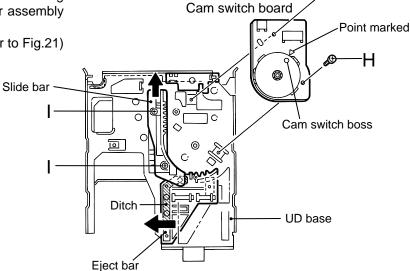

# ■ Removing the cartridge holder assembly (See Fig.14 and 15)

1. Remove the two screws I on the upper side of the loading assembly.

# ■ Removing the slide bar and the eject bar (See Fig.14 and 15)

- Prior to performing the following procedure, remove the cartridge holder assembly.

- 1. Remove the slide bar upward.

- 2. Move the eject bar outward until it stops as shown in Fig.14. Push the convex part g on the bottom of the body and remove the eject bar from the chassis.

Fig.14

Fig.15

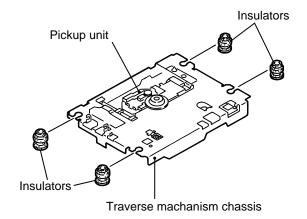

### <Traverse mechanism assembly>

### ■Removing the Insulators (See Fig.16)

1. Disengage the four insulators from the notches of the traverse mechanism chassis.

Fig.16

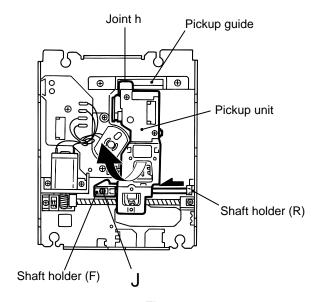

# ■Removing the pickup unit (See Fig.17)

- 1. Turn over the traverse mechanism assembly and remove the screw J attaching the shaft holder (F).

- 2. Move the shaft inward and remove it from the shaft holder (R).

- 3. Detach the shaft side of the pickup unit upward and release the joint h with the pickup guide. Then remove the pickup unit with the shaft.

Fig.17

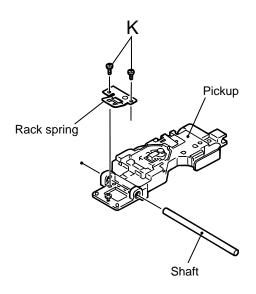

# ■Removing the pickup (See Fig.18)

- 1. Draw out the shaft from the pickup.

- 2. Remove the two screws K attaching the rack spring.

Fig.18

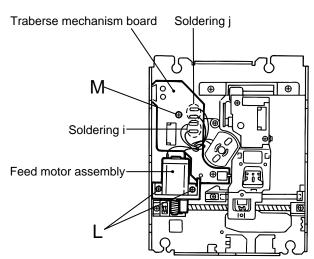

# ■Removing the feed motor assembly (See Fig.19-1, 19-2)

- · It is not necessary to remove the pickup unit.

- 1. For the white and black harnesses extending from the feed motor assembly, unsolder the soldering i on the traverse mechanism board.

- 2. Remove the two screws L attaching the feed motor assembly.

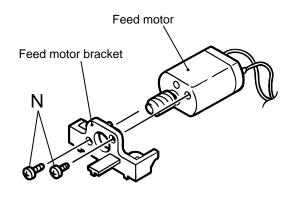

- Remove the two screws N attaching the feed motor bracket.

Fig.19-1

# ■ Removing the traverse mechanism board (See Fig.19-1)

- Prior to performing procedure, remove the feed motor assembly.

- 1. For the red and black harnesses extending from the spindle motor, unsolder the soldering j on the traverse mechanism board.

- 2. Remove the screw M attaching the traverse mechanism board.

Fig.19-2

Ή

### <Reattaching the loading assembly>

1. Reattach the eject bar to the UD base.

(Fig.15 and 20)

- 2. Reattach the slide bar to the loading mechanism chassis while fitting the boss marked k to the eject bar slot. (Fig.20)

- 3. Slide the slide bar and the eject bar in the direction of the arrow in Fig.20 and reattach the cartridge holder assembly using the two screws I.

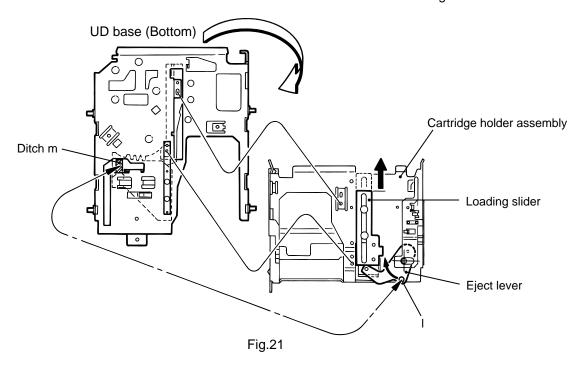

(Fig.20 and 21)

ATTENTION: Make sure the pin of the eject lever marked I is fitted to the slot of the eject bar marked m at the bottom of the loading mechanism chassis after moving the eject lever and the loading slider of the cartridge holder assembly in the direction of the arrow.

(Refer to Fig.21)

Fig.20

### CA-MXS6MDR SP-MXS6MD

- 4. Reattach the wire holder to the UD base while engaging the UD base hook marked u to the wire holder slot marked t (At the same time, the boss on the reverse side of the wire holder is fitted to the UD base round hole).

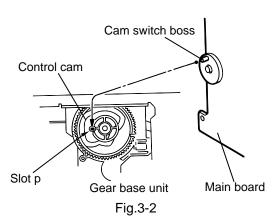

- 5. Reattach the cam switch board using the two screws H. (Fig.22)

- 6. Turn the cam switch to bring the boss to the point marked  $\triangle$  on the cam switch board. Reattach the cam gear using a slit washer while fitting the cam gear slot to the cam switch boss. (Fig.22)

ATTENTION: When reattaching the cam gear, the cam switch boss should be fitted to the cam gear slot, and the triangle mark of the cam gear should be aligned to the hole of the eject bar as shown in Fig.22.

7. Reattach the loading motor assembly, using the screw F. Connect the harness extending from the loading motor to connector CN612 on the switch board and fix it with the wire holder. (Fig.22)

Fig.22

- 8. Reattach the UD base while engaging the four pins on both sides of the UD base to the notches of the loading mechanism base and placing the edge (marked e') of the cartridge holder assembly under the hook e of the loading mechanism base. (Fig.23)

- 9. Reattach the slide base (R) while fitting the two pins on another side of the UD base to the slots of the slide base (R). (Fig.24)

ATTENTION: Fit the part v of the slide base (R) to the part w on the inward side of the cam gear rib. (Fig.25)

10. Reattach the slide base (L) on the slide base (R) while fitting the two pins on another side of the UD base to the slots of the slide base (L) (Fig.25). Make sure the two slots of the slide base (L) are fitted to the two bosses marked E' and tighten the two screws E. (Fig.26)

Ref: To expedite the work, bring up the UD base slightly when fitting each pin to the appropriate notch.

Fig.23

Fig.24

Fig.26

Fig.25

### <CD mechanism section>

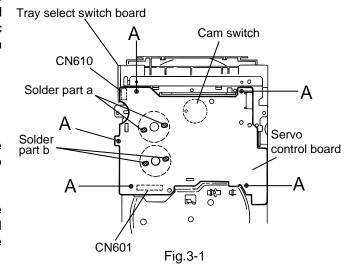

# ■Removing the servo control board (See Fig.1 to 4)

ATTENTION: Make sure the sub chassis unit is locating at the lowest position. If not,perform the following procedure from 1 to 3.

- Insert a screwdriver into the sub chassis slot on the back of the body and push the slider (R) toward the front.

- 2. From the top of the body, slide the hook and the slider (R) forward until they stop.

- From the right side of the body, slide the slide cam

backward until it stops. The sub chassis unit will move to the lowest position.

- 4. From the bottom of the body, unsolder each soldered part a and b of the motors on the servo control board.

- Remove the five screws A attaching the servo control board.

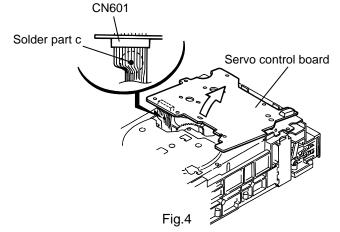

- Disconnect connector CN610 on the servo control board from the tray select switch board to suspend the servo control board tentatively. Solder the part c of the flexible wire connected to connector CN601 on the underside of the servo control board.

- 7. Disconnect the flexible wire from connector CN601 and remove the servo control board from the body.

ATTENTION: In case of disconnecting the flexible wire without soldering, the CD pick up may be damaged.

ATTENTION: When reassembling, make sure the cam switch boss of the servo control board is fitted to the slot p of the control cam on the bottom of the body (Refer to Fig.3-1).

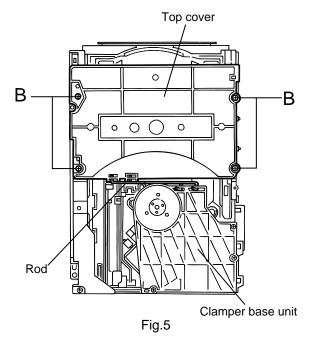

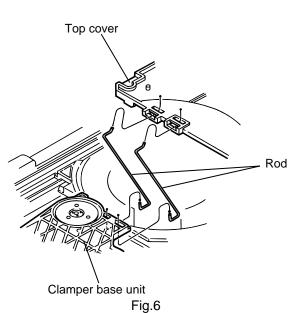

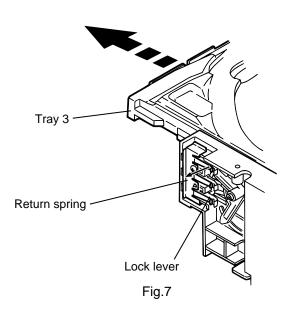

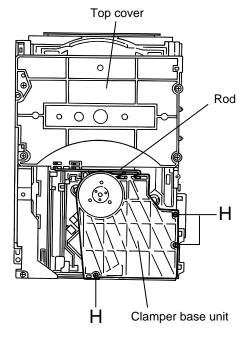

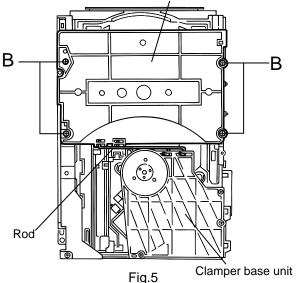

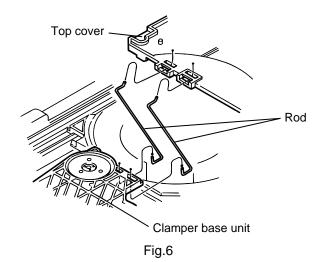

### ■ Removing the tray unit (See Fig.5 to 8)

- \* The tray unit can be removed despite the position of the sub chassis unit, but the lowest position is recommended to expedite the work.

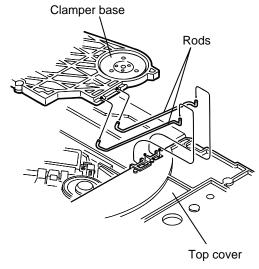

- 1. Remove the four screws B attaching the top cover on the top of the body.

- 2. Remove the top cover with the two rods attached to the top cover and the clamper base unit.

- 3. Pull the lock lever of the return spring on the right side of the body to eject the tray unit.

- 4. From the top of the body, release the tray from the joint hook marked d (Push the tray toward the front).

- 5. Release the stoppers on both sides in the direction of the arrow and pull out the tray unit from the body.

ATTENTION: Pull out the tray unit from the top tray 3 in sequence.

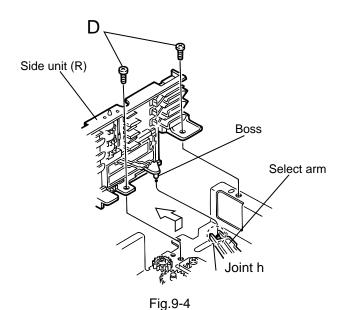

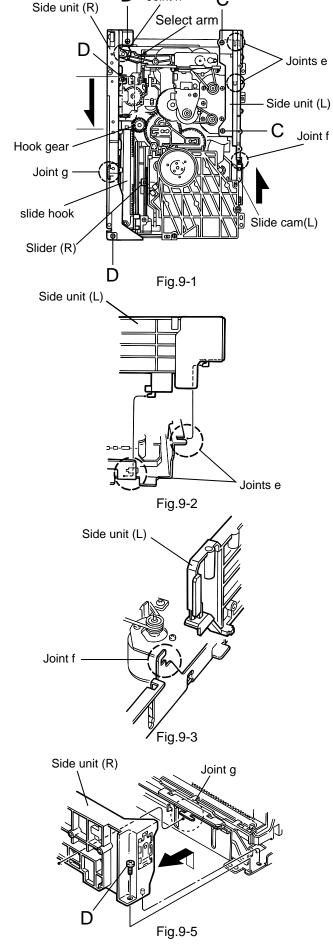

# ■Removing the side unit (L) and (R) (See Fig.9-1 to 9-5)

- Prior to performing the following procedures, remove the servo control board, the top cover and the tray unit.

- 1. Remove the two screws C attaching the side unit (L).

- 2. Slide and remove the side unit (L) toward the front while releasing the two joints e and the joint f with the chassis unit.

- 3. Slide the slide cam (L) toward the front until it stops to place the sub chassis unit at the top position.

ATTENTION: The side unit (R) can be removed when the sub chassis unit is located at the top position.

- 4. Turn the hook gear counterclockwise to move the slide hook and the slider (R) backward until they stop.

- 5. Remove the three screws D attaching the side unit (R). Raise the side unit (R) upward and release the joint g with the chassis unit and the boss from the select arm marked h. Then remove the side unit (R) from the body.

ATTENTION: When reassembling, make sure the boss is fitted to the select arm marked h.

D

Joint h

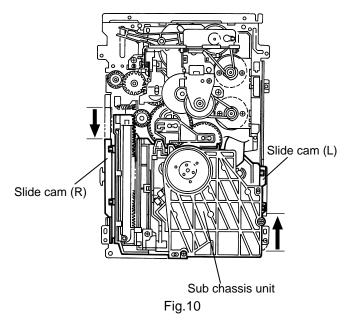

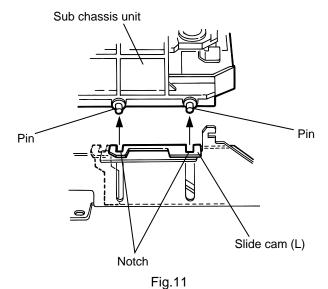

# ■Removing the sub chassis unit (See Fig.10 to 12)

- Prior to performing the following procedures, remove the servo control board, the top cover, the tray unit, the side unit (L) and the side unit (R).

- 1. Turn the hook gear counterclockwise to move the slide hook and the slider (R) backward until they stop.

- 2. Slide the slide cam (L) and the slide cam (R) in the direction of the arrow until they stop.

(The notches of each slide cam are fitted to the pins on both sides of the sub chassis unit.)

3. Detach the sub chassis unit upward.

ATTENTION: When reassembling, turn the hook gear of the chassis unit counterclockwise until it stops and slide the slide hook and the slider (R) of the sub chassis unit backward until they stop.

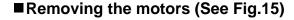

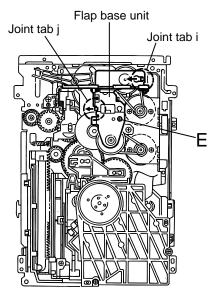

# ■ Removing the flap base unit and the gear base unit (See Fig.13 and 14)

- Prior to performing the following procedures, remove the servo control board, the top cover, the tray unit, the side unit (L) and the side unit (R).

- 1. Remove the screw E attaching the flap base unit. Release the joint tabs i and j, then remove the flap base unit from the body.

- 2. Remove the belts from the two pulleys on the gear base unit.

- 3. Remove the three screws F and remove the gear base unit from the body.

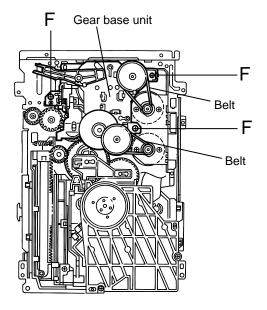

- Prior to performing the following procedure, remove the main board.

- 1. Remove the belts from the two pulleys.

- 2. Remove the four screws G and detach each motor from the body.

Fig.13

Fig.14

Fig.15

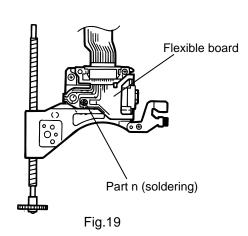

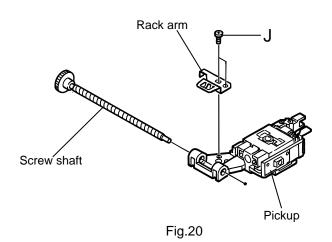

### ■ Removing the pickup (See Fig.16 to 20)

- 1. From the top of the body, remove the three screws H attaching the clamper base unit.

- 2. Remove the clamper base unit with the two rods attached to the clamper base unit and the top cover.

- 3. Turn the screw shaft gear marked k in the direction of the arrow to move the pickup unit.

- 4. Remove the screw I attaching the shaft holder.

- Move the screw shaft in the direction of the arrow and release it from the joint I. Then release it from the joint m with the pickup holder. Detach the pickup with the screw shaft.

- 6. Solder the part n of the flexible board on the underside of the pickup. After soldering, disconnect the flexible wire connected to the pickup (In case of disconnecting the flexible wire without soldering, it may cause damage to the CD pickup).

- 7. Remove the two screws J attaching the rack arm to the pickup unit.

- 8. Pull out the screw shaft from the pickup.

Fig.16

Fig.17

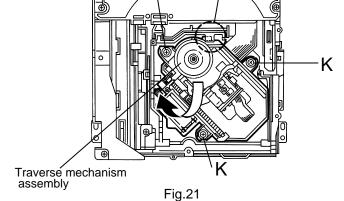

# ■ Removing the traverse mechanism assembly (See Fig.21)

- Prior to performing the following procedure, remove the servo control board and the clamper base unit.

- 1. Remove the three screws K attaching the traverse mechanism assembly.

- Detach the rear part of the traverse mechanism assembly upward to release the joint o with the sub chassis unit. Then remove the assembly from the body.

Traverse mechanism assembly

K

Joint o

# ■ Removing the feed motor (See Fig.22) • Prior to performing the following procedure, rer

- Prior to performing the following procedure, remove the traverse mechanism assembly.

- 1. Remove the screw L attaching the feed motor.

- 1. Remove the four screws B attaching the top cover on the top of the body.

- 2. Remove the top cover with the two rods attached to the top cover and the clamper base unit.

- 3. Remove the screw M on the right side of the body.

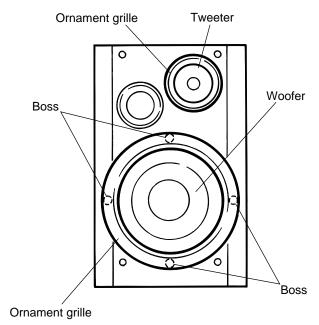

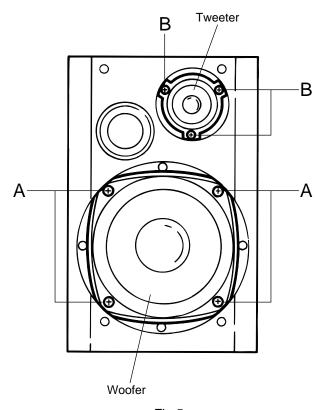

# <Speaker section>

#### Information

This is a method of dis assembly.

As parts of the repair of this speaker system, it is only the speaker box assemblies. It is not possible to supply with each part unit.

Prior to performing the following procedure, remove the front grille.

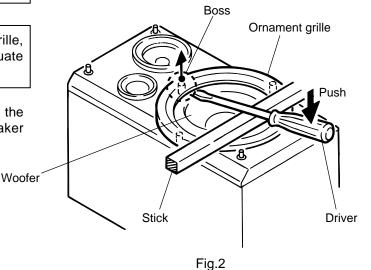

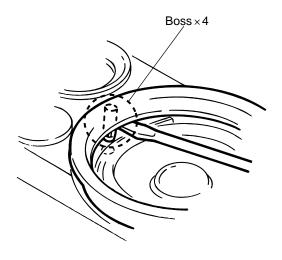

# ■ Removing the speaker (woofer) (See Fig.1,3 to 5)

- 1. Insert a screwdriver under the ornament grille attached to the woofer.

- 2. Pull out the ornament grille with each boss by means of a lever as shown in Fig.2.

ATTENTION: As the ornament grille is damaged, replace it with the woofer.

ATTENTION: When replacing the ornament grille, make sure the boss with adequate amount of bond.

3. Remove the four screws **A** and the woofer from the body. Disconnect the wire from the speaker terminals.

Fig.1

Fig.3

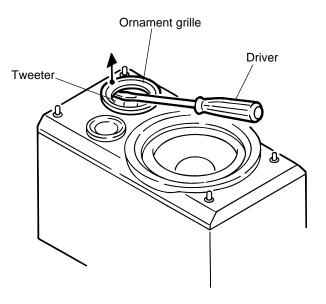

## ■ Removing the speaker (tweeter) (See Fig.4 and 5)

1. Insert a screwdriver under the ornament grille and remove it from the body.

ATTENTION: As the ornament grille is damaged, replace it with the tweeter.

3. Remove the three screws **B** and the tweeter from the body. Disconnect the wire from the speaker terminals.

Fig.4

Fig.5

#### CA-MXS6MDR SP-MXS6MD

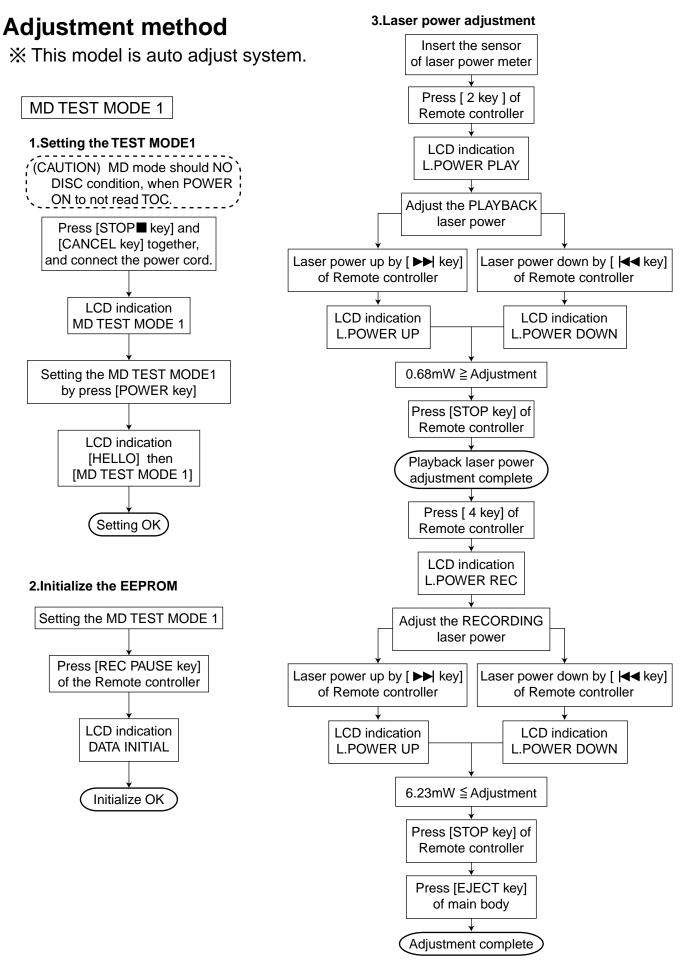

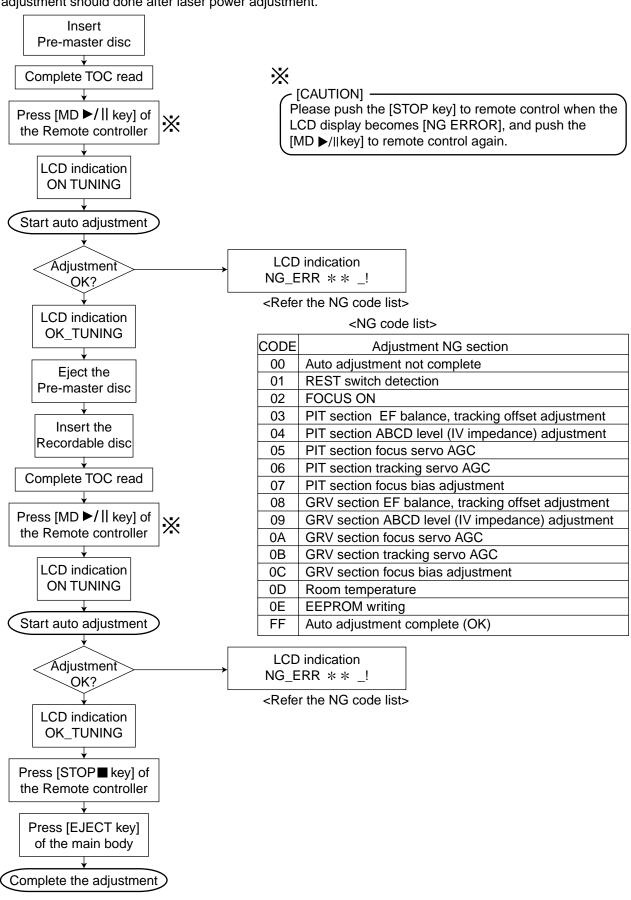

#### 4.Disc adjustment

This adjustment should done after laser power adjustment.

#### 5.Independent operation mode

In case the checking mode or adjustment when occur the error at disc adjustment, Independent mode into by select the key before release the TERST MODE.

| Operation key     |         | MODE           |                    |

|-------------------|---------|----------------|--------------------|

| Remote controller | [SLEEP] | Focus search   | [FOCUS_SEARCH]     |

| Remote controller | [6 key] | Pit rough ser  | vo [P.R.SERVO]     |

| Remote controller | [7 key] | Groove rough s | servo [GR.R.SERVO] |

| Remote controller | [8 key] | Tracking ON    | [TRACKING_ON]      |

| Remote controller | [9 key] | Tracking OFF   | [TRACKING_OFF]     |

| Remote controller | [STOP]  | STOP           | [STOP]             |

| Main body         | [EJECT] | EJECT          | [EJECT]            |

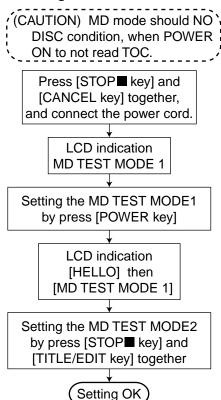

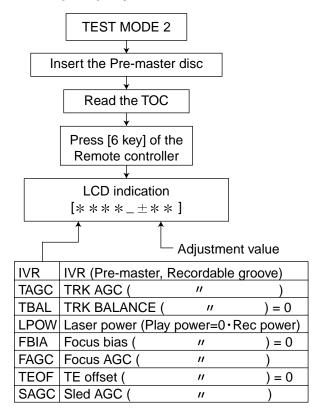

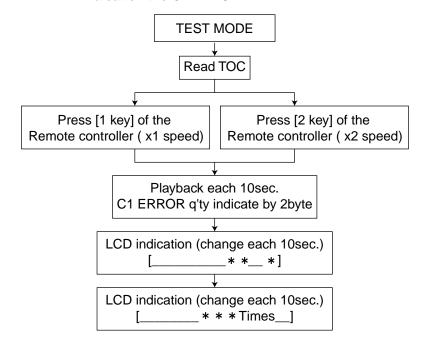

### MD TEST MODE 2

### 1.Setting the TEST MODE 2

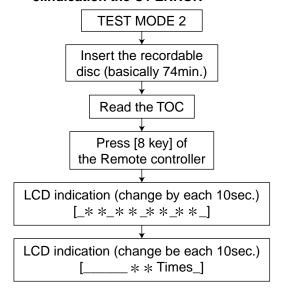

#### 3.Indication the C1 ERROR

# 2.Indication the drift level of the pickup adjustment value

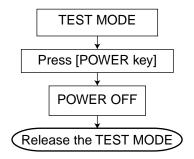

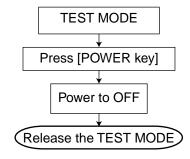

#### 4. Release the MD TEST MODE

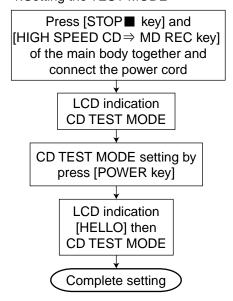

### **CD TEST MODE**

### CD section is no need the adjustment by design.

### 1.Setting the TEST MODE

#### 2.Indication the C1 ERROR

### 3. Release the CD TEST MODE

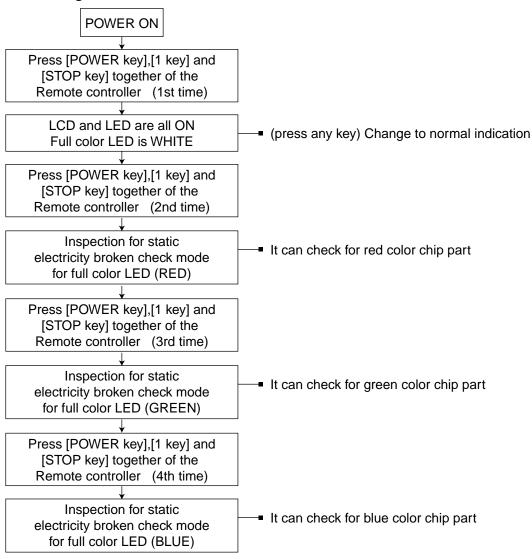

### LCD ALL INDICATION, TIME COMPRESSION TEST MODE

### 1.Setting the TEST MODE

Caution: Full color LED is keep white condition, when loop out by any key at test mode.

#### 2.Fast forward of CLOCK/SLEEP TIMER

Including the ALL LED ON mode and Static electricity broken thes, clock count up is change to 1min. to 1sec.

Check for only [CLOCK mode] and [SLEEP TIMER].

#### 3. Release the TEST MODE

TEST MODE is release by disconnect the AC power cord.

### **RUNNING MODE**

This running mode is a mode by which the recording is compulsorily deleted with ALL-ERASE after U-TOC is written when the recording of MD ends, and the recording is repeated again.

This TEST MODE is continue recording (loop recording), it is for recording stop when MD end.

This TEST MODE is only can use manual operation recording [MD REC PAUSE]. CD synchro recording (CD $\rightarrow$ MD REC,BEST HIT REC,1CD $\rightarrow$  MD REC) is not operate correctly.

#### 1.Setting the TEST MODE

- 1:Setting normal speed recording mode by pressing together [POWER key], [2 key] and [STOP key] of Remote controller.

- 2:If normal speed mode is default then change to high speed mode, press [HIGH SPEED CD>MD key] of main body before recording start.

- 3:Once change to high speed mode, TEST MODE is continue until release.

- 4:Return to normal speed recording mode, it should release the TEST MODE then resetting the TEST MODE.

(REMARKS) Case of CD high speed recording: After setting TEST MODE, if it need setting

CD play mode or repeat mode. Press [HIGH SPEED CD > MD key] setting high speed mode. RUNNING MODE is start by REC STANDBY (indicate [RUNNING MODE] on LCD) at [MD REC PAUSE key] then playback the CD.

(During recording, LCD indicate [RUNNING MODE])

#### 2.Release the TEST MODE

Test mode is release by POWER OFF.

## Indication the [CAUTION !] when abnormal

#### 1. Detect the abnormal condition of stability power supply

Abnormal detection dine of the stability power supply(REG.) at CPU [SAFETY1~3] port (IC801:6,7,9pin), when system CPU (IC801) supply voltage (US D5.6V) is normal condition.

Watching the abnormal at POWER ON condition, if detect the abnormal indicate [CAUTION!] and come under stability power supply (8V/10V or 12V OR 6V), and indicate [DATA(HEX)] of the abnormal port voltage then power off to forcibly.

Detect the abnormal condition of stability power supply is next.

[8V/10V]: SAFETY1 port (Power supply of full color LED/Power supply of CD mechanism)

[12V] : SAFETY2 port (Power supply for tuner module REG, MD mechanism REG, volume IC, LPF IC and CD/MD SELECTOR)

[6V] : SAFETY3 port (Power supply for MD mechanism, power supply for OPT. module, power supply for CD/OPT SELECTOR)

\* (REMARKS) Saféty port voltage at detect the abnormal condition.

| DATA(HEX) | PORT voltage | Detect condition                       |

|-----------|--------------|----------------------------------------|

| 3FF~2D0   | 5.0~3.52V    | Abnormal (Power off at 1sec. forcibly) |

| 2CF~12C   | 3.515~1.456V | Normal                                 |

| 12B~000   | 1.46V~0V     | Abnormal (Power off at 3sec. forcibly) |

#### 2. Abnormal detection of CD mechanism

When detect the abnormal condition of CD mechanism, indicate [CAUTION!] and come under condition and back light is change to [RED] forcibly.

Indication when mechanism abnormal condition.

[CD INITIAL] : Abnormal condition when mechanism initialize after power cord to connect to

AC outlet then power to ON.

[CD MECH] : Abnormal condition when mechanism initialize at return operation, it is

Sub Tray Load/Unload operation, Lifter shift operation, or CAM operation

are defect.

[CD MECHA 5V]: Abnormal condition at 5V (LSI) internal the CD mechanism.

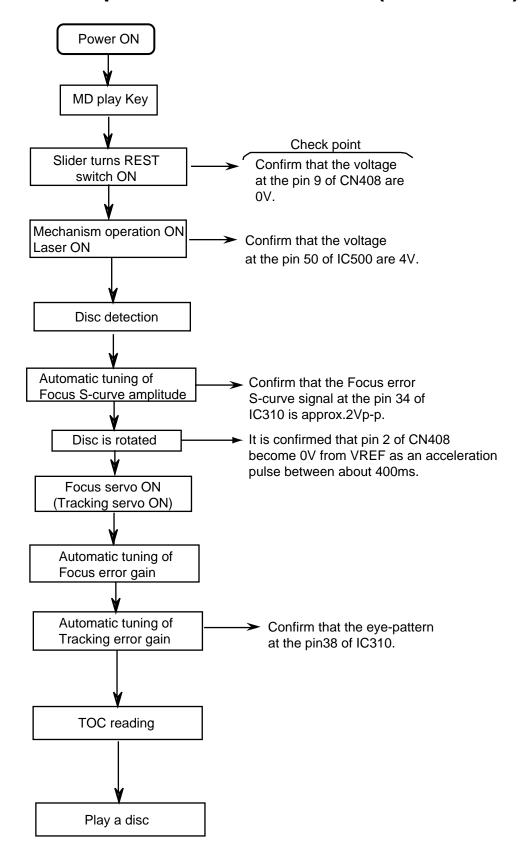

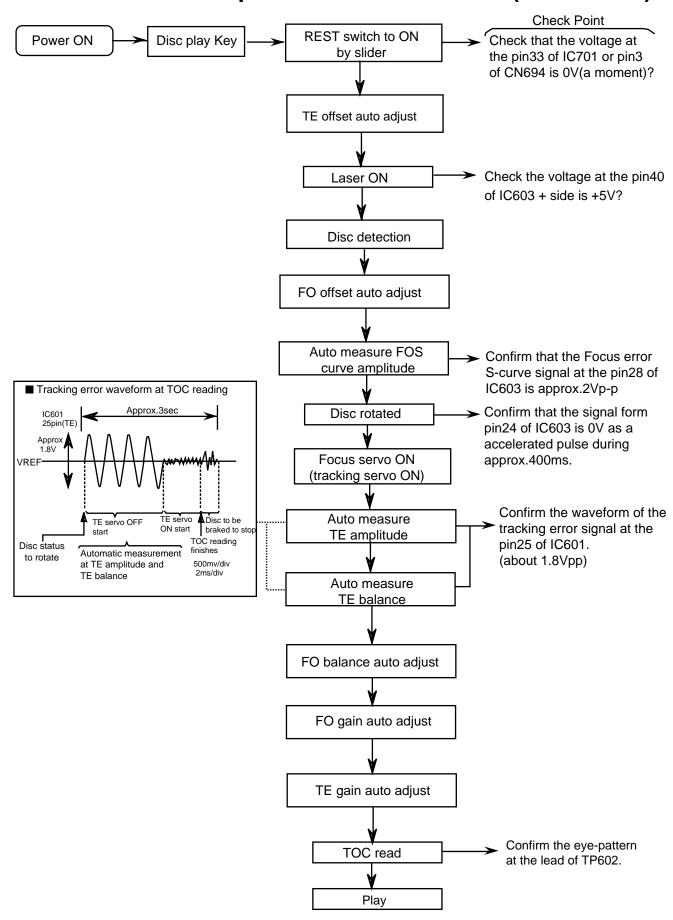

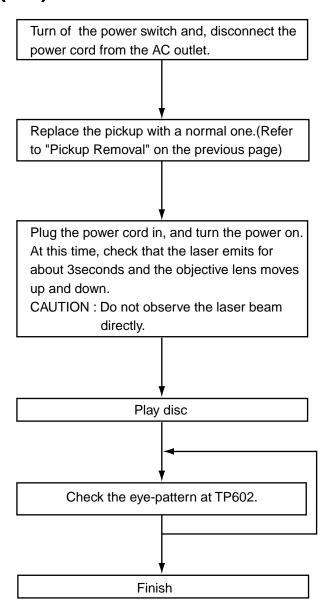

# Flow of functional operation until TOC read (MD section)

# Maintenance of laser pickup (MD)

#### 1. Cleaning of pickup lens

- (1) Prior to changing the pickup, clean the pickup lens.

- (2) For cleaning the lens, use the following cotton swab after mearsing it in alcohol.

Product No: JCB-B4 Manufacturer: Nippon Cotton Swab

- 2. Confirmation of the service life of laser diode when the service life of the laser diode has been exhausted, the following symptoms will appear.

- (1) Recording will become impossible.

- (2) The RF output (EFM output and eye-pattern amplitude) will become lower.

- (3) The drive current required for light emitting of laser diode will be increased.

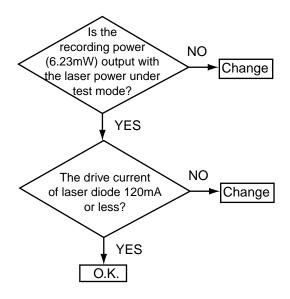

Confirm the service life according to the following flow chart.

# 3. Method of measuring the drive current of laser diode

When the voltage measured at each side of R337, it become 120mV or over, the service life of laser diode is judged to have been exhausted.

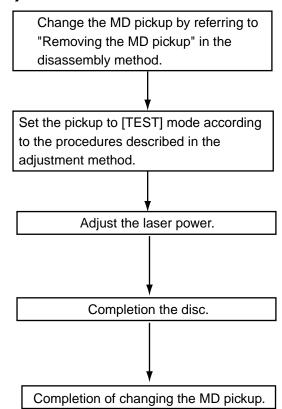

# Replacement of laser pickup (MD)

#### CAUTION

Since this system is designed to perform magnetic recording, the laser power ten times or over of the conventional MD player will be output. Therefore, be sure to perform not only adjustment and operation of this system so carefully as not to directly look at the laser beam or touch on the body.

# 4.Semi-solid state resistors on the APC board.

The semi-solid state resistor on the APC board attached to the pickup is used for adjusting the laser power. Since these resistor should be adjusted in pair according to the characteristics of the optical block, be sure not touch on the resistors. Since the service life of the laser diode will be exhausted when the laser power is low, it is necessary to change the pickup. Meanwhile, do not pickup. Otherwise, the pickup will be damaged due to over current.

# Flow of functional operation until TOC read (CD section)

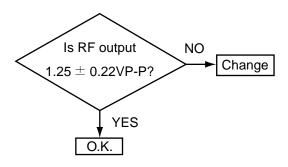

# Maintenance of laser pickup (CD)

- (1) Cleaning the pickup lens Before you replace the pickup, please try to clean the lens with a alcohol soaked cotton swab.

- (2) Life of the laser diode

When the life of the laser diode has expired,

the following symptoms will appear.

- (1) The level of RF output (EFM output : amplitude of eye-pattern) will below.

(3) Semi-fixed resistor on the APC board The semi-fixed resistor on the APC board which is attached to the pickup is used to adjust the laser power.

Since this adjustment should be performed to match the characteristics of the whole optical block, do not touch the semi-fixed resistor.

If the laser power is lower than specified value, the laser diode is almost worm out, and the pickup should be replaced. If the semi-fixed resistor is adjust while the pickup is functioning normally, the laser pickup may be damaged due to excessive current.

# Replacement of laser pickup (CD)

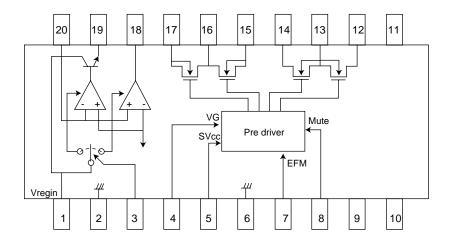

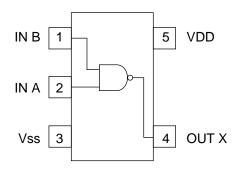

# **Description of major ICs**

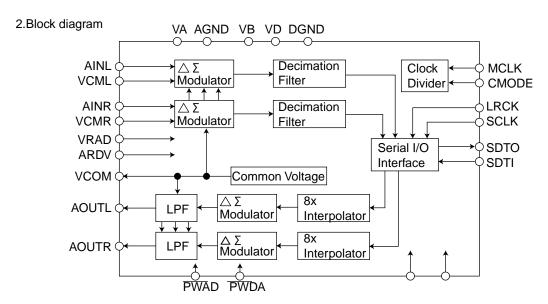

### ■ AK4519VF-X (IC480) : A / D D / A converter

| Pin<br>NO. | Symbol | I/O | Function                                |

|------------|--------|-----|-----------------------------------------|

| 1          | VRDA   |     | Voltage Reference Input Pin for DAC, VA |

| 2          | VRAD   | ı   | Voltage Reference Input Pin for ADC, VA |

| 3          | AINR   |     | RCH Analog Input Pin                    |

| 4          | VCMR   | 0   | Rch Common Voltage Output Pin, 0.45xVA  |

| 5          | VCML   | 0   | Lch Common Voltage Output Pin, 0.45xVA  |

| 6          | AINL   | _   | Lch Analog Input Pin                    |

| 7          | PWAD   | ı   | ADC Power-Down Mode Pin "L":Power Down  |

| 8          | PWDA   | _   | DAC Power-Down Mode Pin "L":Power Down  |

| 9          | MCLK   | ı   | Master Clock Input Pin                  |

| 10         | LRCK   | -   | Input/Output Channel Clock Pin          |

| 11         | SCLK   | ı   | Audio Serial Data Clock Pin             |

| 12         | SDTO   | 0   | Audio Serial Data Output Pin            |

| 13         | DGND   | -   | Digital Ground Pin                      |

| 14         | VD     | -   | Digital Power Supply Pin                |

| 15         | SDTI   | I   | Audio Serial Data Input Pin             |

| 16         | CMODE  | ı   | Master Clock Select Pin                 |

| 17         | DEM1   | - 1 | De-emphasis Frequency Select Pin        |

| 18         | DEM0   | ı   | De-emphasis Frequensy Select Pin        |

| 19         | AOUTL  | 0   | Lch Analog Output Pin                   |

| 20         | AOUTR  | 0   | Rch Analog Output Pin                   |

| 21         | VCOM   | 0   | Common Voltage Output Pin, 0.45xVA      |

| 22         | AGND   | -   | Analog Ground Pin                       |

| 23         | VB     | -   | Substrate Pin                           |

| 24         | VA     | -   | Analog Power Supply Pin                 |

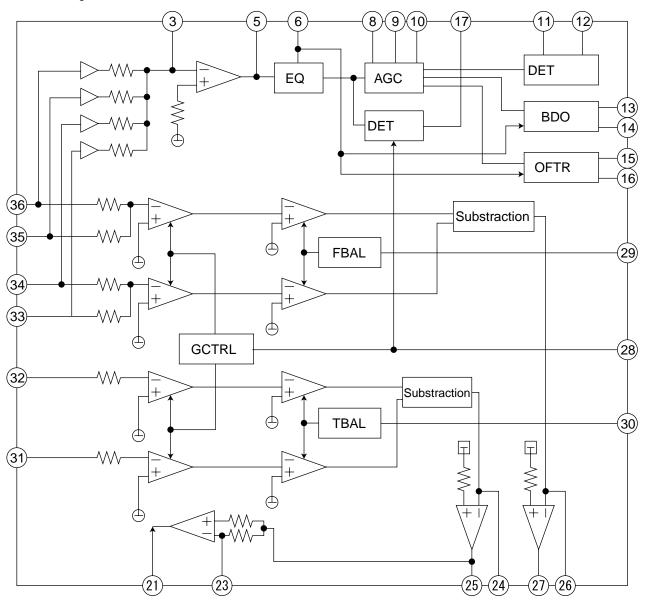

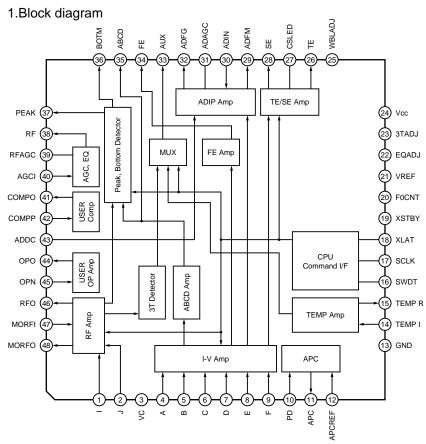

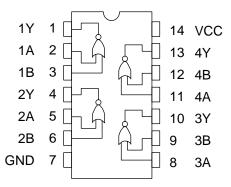

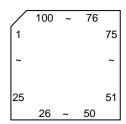

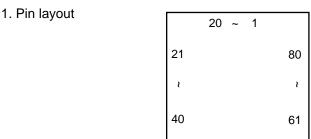

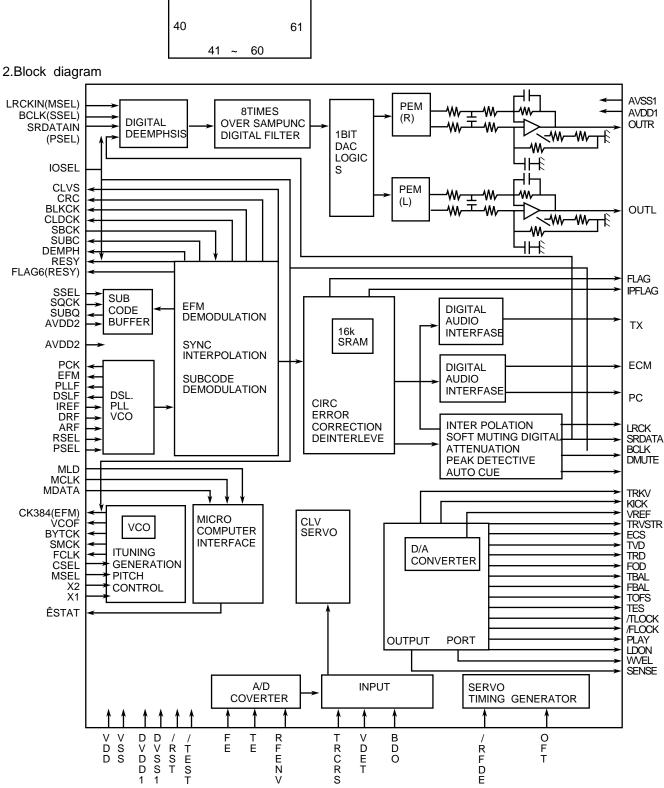

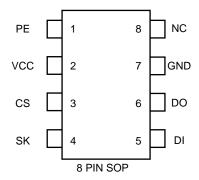

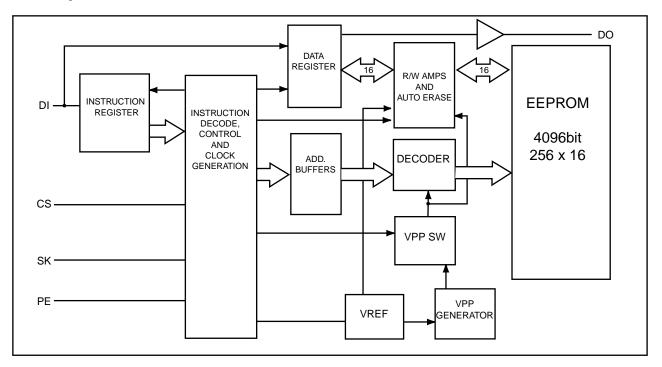

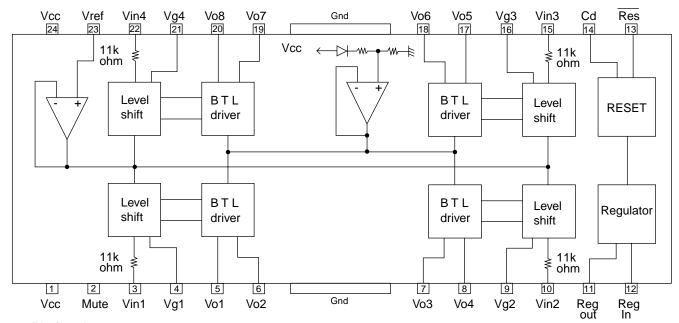

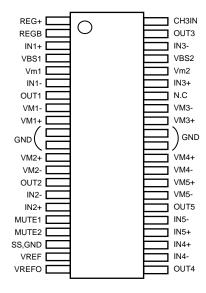

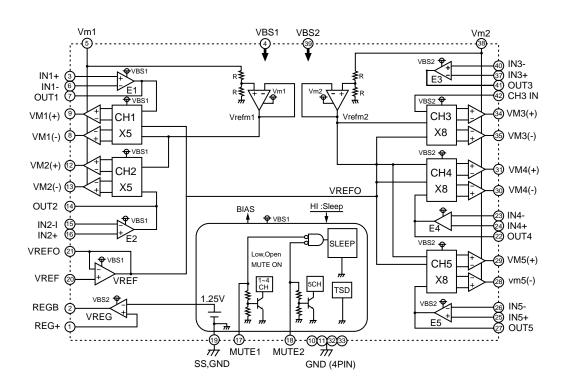

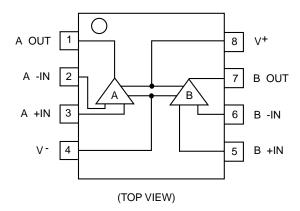

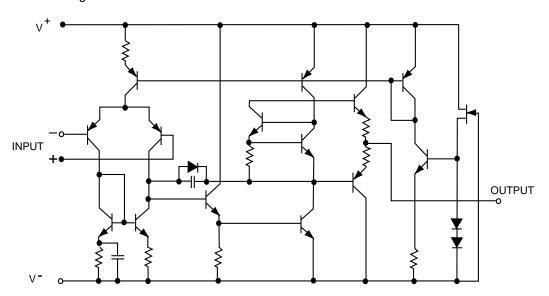

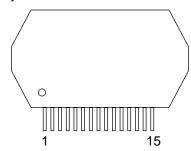

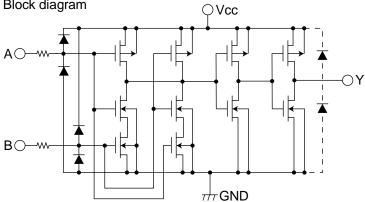

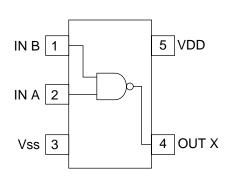

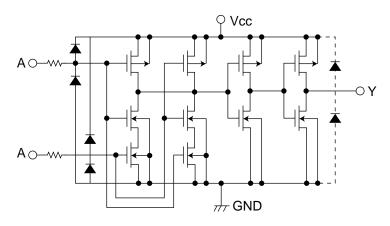

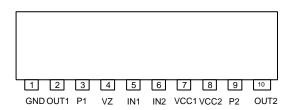

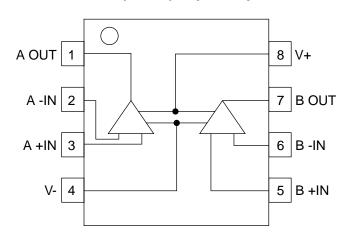

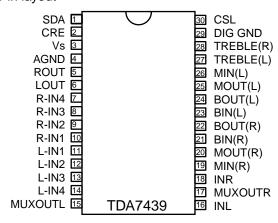

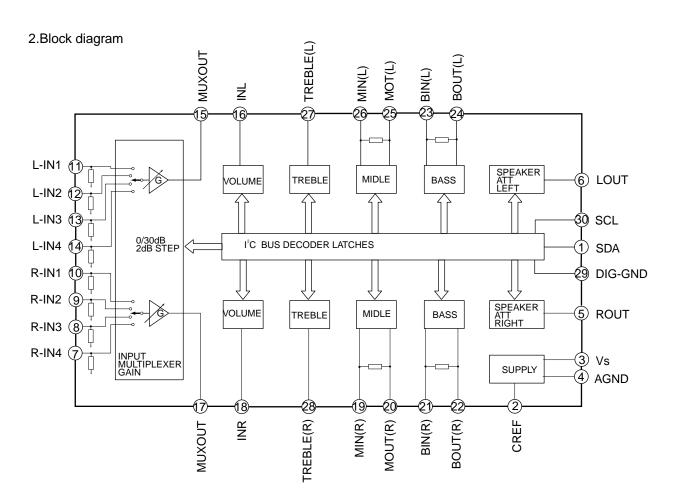

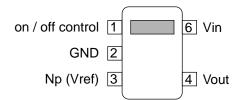

## ■ AN8849SB-W (IC601) : Head amp

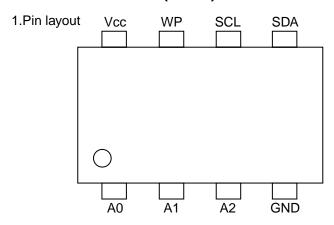

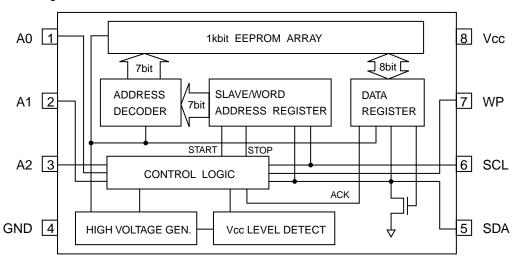

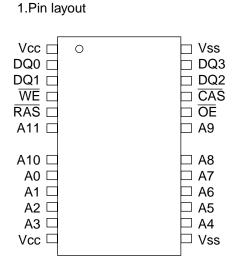

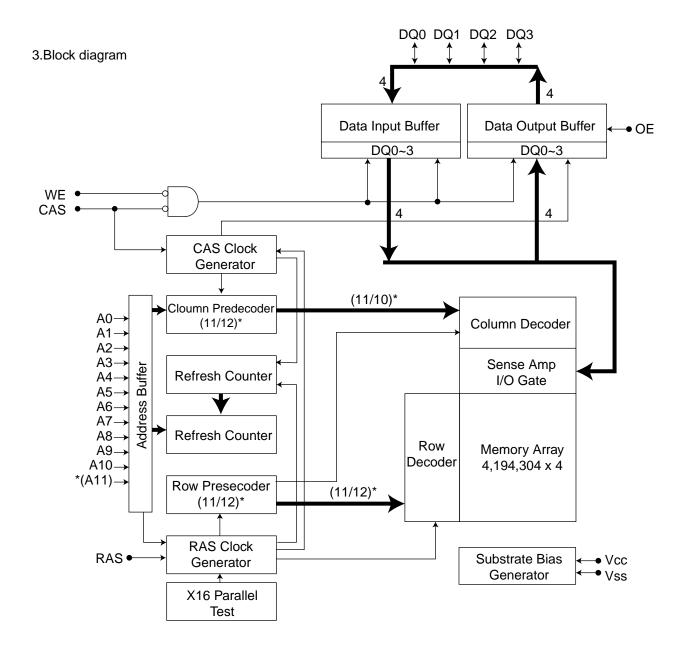

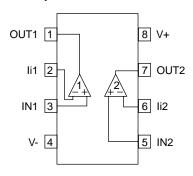

#### 1.Pin layout

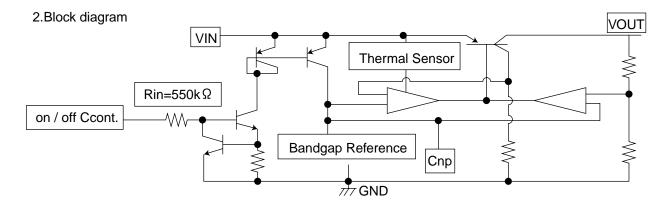

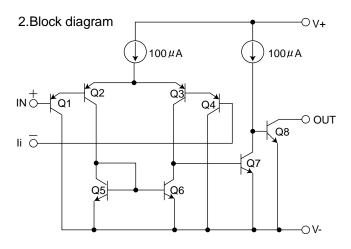

#### 2.Block diagram

| Pin<br>NO. | Symbol | Function                                                        |

|------------|--------|-----------------------------------------------------------------|

| 1          | PD     | Photo detector signal input.                                    |

| 2          | LD     | Laser diode drive terminal.                                     |

| 3          | RFN    | RF amp negative input terminal.                                 |

| 4          | Vcc1   | Power supply terminal.                                          |

| 5          | RFOUT  | Equaruzer connect terminal.                                     |

| 6          | EQSW   | Power supply terminal.                                          |

| 7          | Vcc2   | RF AGC input terminal.                                          |

| 8          | RFC    | RF AGC filter connect terminal.                                 |

| 9          | CAGC   | ARF output terminal.                                            |

| 10         | ARF    | 3T envelope detect filter terminal.                             |

| 11         | CEA    | Envelope detect output circuit.                                 |

| 12         | ENV    | Low level DO detect connect terminal.                           |

| 13         | CBDO   | DO detect signal output terminal.                               |

| 14         | BDO    | OFF TRACK detect signal connect terminal.                       |

| 15         | COFTR  | OFF TRACK detect signal output terminal.                        |

| 16         | OFTR   | RF signal amp. detection output.                                |

| 17         | NRFDET | Ground.                                                         |

| 18         | GND    | LD APC ON / OFF select.                                         |

| 19         | LDON   | Reference voltage output terminal.                              |

| 20         | VREF1  | CROSS detect signal output terminal.                            |

| 21         | CROSS  | Reference voltage output terminal.                              |

| 22         | VREF2  | CROSS detect filter connect terminal.                           |

| 23         | CCRS   | Tracking error output terminal.                                 |

| 24         | TEN    | TE amp.negative input terminal.                                 |

| 25         | TEOUT  | FE amp.negative input terminal.                                 |

| 26         | FEN    | Focus error output terminal.                                    |

| 27         | FEOUT  | Focus gain, tracking gain adjust control signal inout terminal. |

| 28         | GCTRL  | Focus barance adjust control input terminal.                    |

| 29         | FBAL   | Tracking barance adjust control input terminal.                 |

| 30         | TBAL   | Connect PDIC.                                                   |

| 31         | E      | Connect PDIC.                                                   |

| 32         | F      | Connect PDIC.                                                   |

| 33         | D      | Connect PDIC.                                                   |

| 34         | В      | Connect PDIC.                                                   |

| 35         | С      | Connect PDIC.                                                   |

| 36         | Α      | Connect PDIC.                                                   |

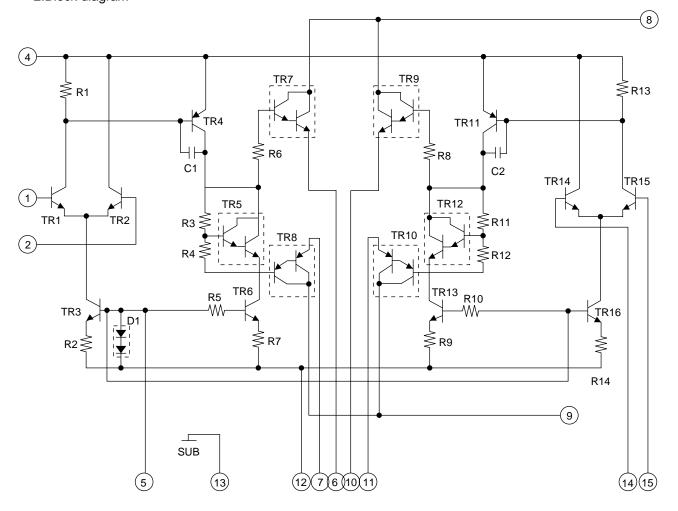

#### ■ CXA2523AR (IC310): MD servo

| Pin No. | Symbol | I/O | Function                                                                |  |  |  |  |

|---------|--------|-----|-------------------------------------------------------------------------|--|--|--|--|

| 1       | I      | Ι   | I-V converted RF signal I input.                                        |  |  |  |  |

| 2       | J      | I   | I-V converted RF signal J input.                                        |  |  |  |  |

| 3       | VC     | 0   | Vcc/2 voltage output.                                                   |  |  |  |  |

| 4       | Α      | ı   | A current input for main beam servo signal.                             |  |  |  |  |

| 5       | В      | ı   | B current input for main beam servo signal.                             |  |  |  |  |

| 6       | С      | I   | C current input for main beam servo signal.                             |  |  |  |  |

| 7       | D      | ı   | D current input for main beam servo signal.                             |  |  |  |  |

| 8       | Е      | ı   | E current input for side beam servo signal.                             |  |  |  |  |

| 9       | F      | ı   | F current input for side beam servo signal.                             |  |  |  |  |

| 10      | PD     | ı   | Reflection light quantity monitor signal input.                         |  |  |  |  |

| 11      | APC    | 0   | Laser APC output.                                                       |  |  |  |  |

| 12      | APCREF | ı   | Reference voltage input for the laser power intensity setting.          |  |  |  |  |

| 13      | GND    | -   | Connect to GND.                                                         |  |  |  |  |

| 14      | TEMPI  | ı   | Connects the temperature sensor.                                        |  |  |  |  |

| 15      | TEMP R | ı   | Connects the temperature sensor. outputs the reference voltage.         |  |  |  |  |

| 16      | SWDT   | -   | Data input for microcomputer serial interface.                          |  |  |  |  |

| 17      | SCLK   | ı   | Shift clock input for microcomputer serial interface.                   |  |  |  |  |

| 18      | XLAT   | I   | Latch signal input for microcomputer serial interface.Latched when low. |  |  |  |  |

| 19      | XSTBY  | I   | Standby setting pin. Normal operation when high Standby when low.       |  |  |  |  |

| 20      | F0CNT  | Ι   | Internal current source setting pin.                                    |  |  |  |  |

| Pin No. | Symbol | I/O | Function                                                                  |  |  |  |

|---------|--------|-----|---------------------------------------------------------------------------|--|--|--|

| 21      | VREF   | 0   | Reference voltage output.                                                 |  |  |  |

| 22      | EQADJ  | I/O | Equalizer center frequency setting pin.                                   |  |  |  |

| 23      | 3TADJ  | I/O | BPF3T center frequency setting pin.                                       |  |  |  |

| 24      | Vcc    | -   | Power supply.                                                             |  |  |  |

| 25      | WBLADJ | I/O | BPF22 center frequency setting pin.                                       |  |  |  |

| 26      | TE     | 0   | Tracking error signal output.                                             |  |  |  |

| 27      | CSLED  | -   | Connects the sled error signal LPF capacitor.                             |  |  |  |

| 28      | SE     | 0   | Sled error signal output.                                                 |  |  |  |

| 29      | ADFM   | 0   | ADIP FM signal output.                                                    |  |  |  |

| 30      | ADIN   | I   | ADIP signal comparator input.                                             |  |  |  |

| 31      | ADAGC  | -   | Connects the ADIPAGC capacitor.                                           |  |  |  |

| 32      | ADFG   | 0   | ADIP2 binary value signal output.                                         |  |  |  |

| 33      | AUX    | 0   | 13 output / temperature signal output. Switched with serial commands.     |  |  |  |

| 34      | FE     | 0   | Focus error signal output.                                                |  |  |  |

| 35      | ABCD   | 0   | Reflection light quantity signal output for the main beam servo detector. |  |  |  |

| 36      | BOTM   | 0   | RF/ABCD bottom hold signal output.                                        |  |  |  |

| 37      | PEAK   | 0   | Peak hold signal output for the RF/ABCD signals.                          |  |  |  |

| 38      | RF     | 0   | RF equalizer output.                                                      |  |  |  |

| 39      | RFAGC  | -   | Connects the RFAGC capacitor.                                             |  |  |  |

| 40      | AGCI   | ı   | RFAGC input.                                                              |  |  |  |

| 41      | COMPO  | 0   | User comparator output.                                                   |  |  |  |

| 42      | COMPP  | I   | User comparator non-inverted input.                                       |  |  |  |

| 43      | ADDC   | I/O | Connects the capacitor for ADIP amplifier feedback circuit.               |  |  |  |

| 44      | OPO    | 0   | User operational amplifier output.                                        |  |  |  |

| 45      | OPN    | I   | User operational amplifier inverted input.                                |  |  |  |

| 46      | RFO    | 0   | RF amplifier output. Eye pattern checkpoint.                              |  |  |  |

| 47      | MORFI  | ı   | Input of the groove RF signal with AC coupling.                           |  |  |  |

| 48      | MORFO  | 0   | Groove RF signal output.                                                  |  |  |  |

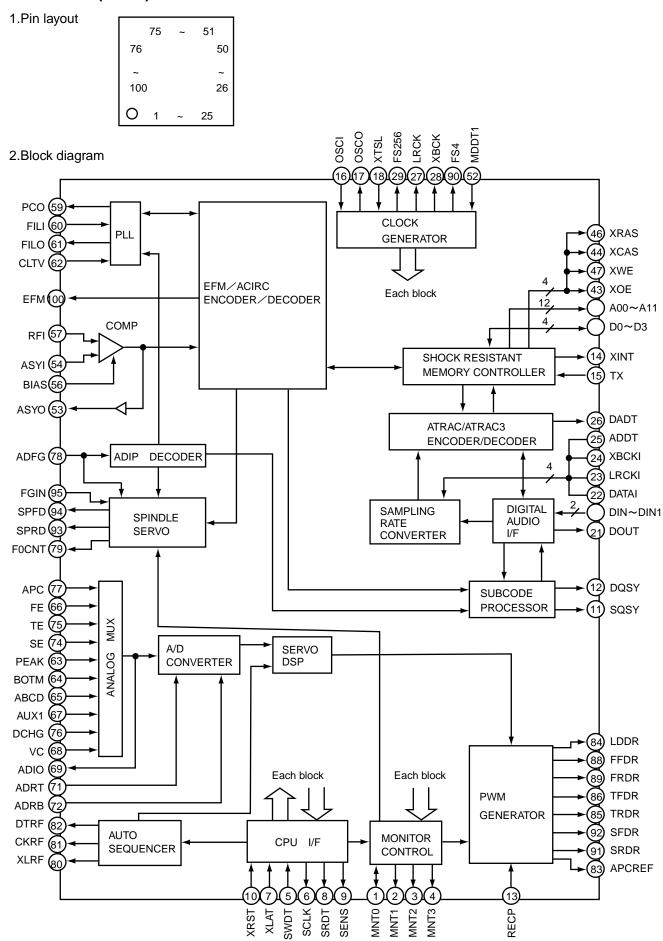

#### ■ CXD2662R (IC350) : DSP

| Pin No. Symbol I/O Monitor output.  1 MNT0 I/O Monitor output.  2 MNT1 O Monitor output.  3 MNT2 O Monitor output.  4 MNT3 O Monitor output.  5 SWDT I Data input for microcomputer serial interface.  6 SCLK I Shift clook input for microcomputer serial interface.  7 XLAT I Latch input for microcomputer serial interface.  8 SRDT O Data output for microcomputer serial interface.  9 SENS O Outputs the internal status corresponding to the microcomputer interface address.  10 XRST I Reset input. Low: reset  11 SQSY O Disc subcode Q sync / ADIP sync output.  12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  13 RECP I Laser power switching input.  High: recording power; low; playback power  14 XINT O Interruption request output. Low when the interruption status occurs in the property of the property in the property in the property input.  15 TX I Enable signal input for recoding data output. High: enabled | serial |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2 MNT1 O Monitor output. 3 MNT2 O Monitor output. 4 MNT3 O Monitor output. 5 SWDT I Data input for microcomputer serial interface. 6 SCLK I Shift clook input for microcomputer serial interface. 7 XLAT I Latch input for microcomputer serial interface. Latched at the falli 8 SRDT O Data output for microcomputer serial interface. 9 SENS O Outputs the internal status corresponding to the microcomputer interface address. 10 XRST I Reset input. Low: reset 11 SQSY O Disc subcode Q sync / ADIP sync output. 12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD. 13 RECP I Laser power switching input. 14 High: recording power; low; playback power 15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                             | serial |

| 3 MNT2 O Monitor output. 4 MNT3 O Monitor output. 5 SWDT I Data input for microcomputer serial interface. 6 SCLK I Shift clook input for microcomputer serial interface. 7 XLAT I Latch input for microcomputer serial interface. Latched at the falli SRDT O Data output for microcomputer serial interface. 9 SENS O Outputs the internal status corresponding to the microcomputer interface address. 10 XRST I Reset input. Low: reset 11 SQSY O Disc subcode Q sync / ADIP sync output. 12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD. 13 RECP I Laser power switching input. 14 XINT O Interruption request output. Low when the interruption status occurs. 15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                      | serial |

| 4 MNT3 O Monitor output.  5 SWDT I Data input for microcomputer serial interface.  6 SCLK I Shift clook input for microcomputer serial interface.  7 XLAT I Latch input for microcomputer serial interface. Latched at the falli  8 SRDT O Data output for microcomputer serial interface. Latched at the falli  8 SRDT O Data output for microcomputer serial interface.  9 SENS O Outputs the internal status corresponding to the microcomputer interface address.  10 XRST I Reset input. Low: reset  11 SQSY O Disc subcode Q sync / ADIP sync output.  12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  13 RECP I Laser power switching input.  High: recording power; low; playback power  14 XINT O Interruption request output. Low when the interruption status occurs.  15 TX I Enable signal input for recoding data output. High: enabled                                                                                       | serial |

| 5 SWDT I Data input for microcomputer serial interface. 6 SCLK I Shift clook input for microcomputer serial interface. 7 XLAT I Latch input for microcomputer serial interface.Latched at the falli 8 SRDT O Data output for microcomputer serial interface.Latched at the falli 8 SRDT O O Data output for microcomputer serial interface. 9 SENS O Outputs the internal status corresponding to the microcomputer interface address. 10 XRST I Reset input. Low: reset 11 SQSY O Disc subcode Q sync / ADIP sync output. 12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD. 13 RECP I Laser power switching input. High: recording power; low; playback power 14 XINT O Interruption request output. Low when the interruption status occ 15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                 | serial |

| 6 SCLK I Shift clook input for microcomputer serial interface.  7 XLAT I Latch input for microcomputer serial interface. Latched at the falli  8 SRDT O Data output for microcomputer serial interface.  9 SENS O Outputs the internal status corresponding to the microcomputer interface address.  10 XRST I Reset input. Low: reset  11 SQSY O Disc subcode Q sync / ADIP sync output.  12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  13 RECP I Laser power switching input.  14 High: recording power; low; playback power  15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                                       | serial |

| 7 XLAT I Latch input for microcomputer serial interface.Latched at the falli 8 SRDT O Data output for microcomputer serial interface.  9 SENS O Outputs the internal status corresponding to the microcomputer interface address.  10 XRST I Reset input. Low: reset  11 SQSY O Disc subcode Q sync / ADIP sync output.  12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  13 RECP I Laser power switching input. High: recording power; low; playback power  14 XINT O Interruption request output. Low when the interruption status occurs.  15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                            | serial |

| 8 SRDT O Data output for microcomputer serial interface.  9 SENS O Outputs the internal status corresponding to the microcomputer interface address.  10 XRST I Reset input. Low: reset  11 SQSY O Disc subcode Q sync / ADIP sync output.  12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  13 RECP I Laser power switching input. High: recording power; low; playback power  14 XINT O Interruption request output. Low when the interruption status occurs.  15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                                                                                                         | serial |

| 9 SENS O Outputs the internal status corresponding to the microcomputer interface address.  10 XRST I Reset input. Low: reset  11 SQSY O Disc subcode Q sync / ADIP sync output.  12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  13 RECP I Laser power switching input. High: recording power; low; playback power  14 XINT O Interruption request output. Low when the interruption status occurs.  15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| interface address.  I Reset input. Low: reset  I SQSY O Disc subcode Q sync / ADIP sync output.  DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  RECP I Laser power switching input. High: recording power; low; playback power  XINT O Interruption request output. Low when the interruption status occurs.  I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| 11 SQSY O Disc subcode Q sync / ADIP sync output.  12 DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  13 RECP I Laser power switching input. High: recording power; low; playback power  14 XINT O Interruption request output. Low when the interruption status occurs.  15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | al In  |

| DQSY O Subcode Q sync output in U-bit CD or MD format when the Digit source is CD or MD.  Laser power switching input. High: recording power; low; playback power  XINT O Interruption request output. Low when the interruption status occurs TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | al In  |

| source is CD or MD.  13 RECP I Laser power switching input. High: recording power; low; playback power  14 XINT O Interruption request output. Low when the interruption status occurs. TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | al In  |

| 13 RECP I High: recording power; low; playback power  14 XINT O Interruption request output. Low when the interruption status occ  15 TX I Enable signal input for recoding data output. High: enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| 15 TX I Enable signal input for recoding data output. High : enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | curs.  |

| 16 OSCI I Crystal oscillation circuit input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| 10   0001   1   Oryotal oscillation circuit input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 17 OSCO O Crystal oscillation circuit output. (inverted output ofthe OSCI pin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )      |

| OSCI input frequency switching.  XTSL1(command) = low and XTSL = high : 512Fs (22.5792MHz XTSL1(command) = low and XTSL = low : 1024Fs (45.1584MHz XTSL1(command) = high : 2048Fs (90.3168MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 19 DIN0 I Digital audio interface signal input 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| 20 DIN1 I Digital audio interface signal input 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| 21 DOUT O Digital audio interface signal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 22 DATAI I Test pin. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |